Croisière au coeur d'un OS Etape 4 : La pagination

x86 : adresse linéaire

Espaces dadresses fictif et physique

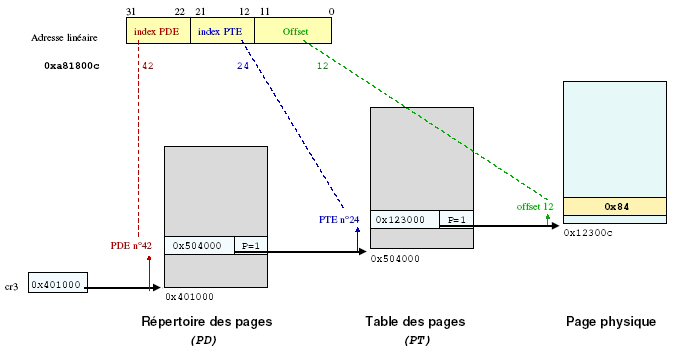

Les tables de traduction dadresses pour la pagination permettent à la MMU de traduire les adresses fictives de début des pages, en adresses des pages en RAM. La pagination sur larchitecture x86 permet de traduire des adresses linéaires sur 32 bits vers des adresses physiques sur 32 bits (ie on peut accéder à 4 Go de RAM au maximum), avec des pages de 4 Ko. Lorsque la MMU ne trouve aucune traduction en adresse physique ou détecte un problème de droit daccès, elle signale lexception 14 Page Fault au processeur. Les tables de traduction dadresses sont des tables à deux niveaux dindirection, la table de premier niveau permettant daccéder aux tables du second niveau.

Nous avons ici un exemple avec l'adresse linéaire 0xa81800c traduite en adresse physique 0x12300c et contenant la valeur 84. Pour obtenir cette traduction nous passons dans le répertoire des tables (PD) et dans la table des pages (PT). Nous expliquerons leur fonctionnement dans la page suivante.

En fait, larchitecture x86 supporte dautres types de tables de traduction : à 3 niveaux avec lextension PAE; à 4 niveaux dans larchitecture x86-64. Il supporte aussi dautres tailles de pages (4Mo ou 2Mo avec lextension PSE et/ou PAE) et des adresses physiques sur 36 bits au lieu de 32 (extension PAE). Aucune de ces extensions n'est utilisé dans SOS, donc nous nen parlerons pas dans ce qui suit. Dans tous les cas, sur x86, toutes les tables de traduction dadresses se situent dans la RAM.

Décomposition d'une adresse linéaire

Une adresse linéaire (32 bits) se décompose de la façon suivante pour la partie pagination de la MMU :

- bits 31-22 : Lindex dans la table de premier niveau, où est stockée ladresse de début de la table de second niveau en RAM;

- bits 12-21 : Lindex dans la table de second niveau, où est stockée ladresse de début de la page en RAM;

- bits 0-11 : Le déplacement dans la page.

le TLB

Comme vous avez pu le ramarquer pour traduire une adresse linéaire

en adresse physique il faut faire trois opération de lecture dans la mémoire.

La premiere dans la table de premier niveau, la deuxieme dans la table de second niveau

et finalement la troisième pour récupérer la donnée.

La MMu dispose d'un cache de traduction appelé TLB contenant,

selon les processeurs, 30 à quelque centaine de traduction

adresse linéaire => adresse physique.

Une traduction complète (3 lectures) sera donc stocker dans ce cache permettant à la prochaine

demande de traduction de diminuer le nombre de lecture. Ce système permet donc de mimiser l'utilisation

d'une traduction complète et d'accélérer le processus.

page suivante >